# 8 GHz to 14 GHz, Low Noise Amplifier

### **FEATURES**

- ▶ Single positive supply (self biased) typical: 1.5 V and 35 mA

- ► RBIAS drain current adjustment pin

- ▶ Gain: 28.5 dB from 8 GHz to 10 GHz

- Noise figure: 1 dB from 8 GHz to 10 GHz

- ► Extended operating temperature range: -55°C to +125°C

- ▶ Internally matched and AC-coupled

- ▶ RoHS-compliant, 2 mm × 2 mm, 8-lead LFCSP

#### **APPLICATIONS**

- ▶ Satellite communications

- ▶ Radar

- ▶ Telecommunications

#### **GENERAL DESCRIPTION**

The ADL8143 is a low noise amplifier (LNA) that operates from 8 GHz to 14 GHz. The typical gain, noise figure, output power for 1 dB compression (OP1dB), and output third-order intercept (OIP3) are 28.5 dB, 1 dB, 7.5 dBm, and 19.5 dBm, respectively, from 8 GHz to 10 GHz. The nominal quiescent current (IDQ), which can be adjusted, is 35 mA from a 1.5 V supply voltage (VDD). The ADL8143 also features inputs and outputs that are AC-coupled and internally matched to 50  $\Omega$ .

The ADL8143 is housed in an RoHS-compliant,  $2 \text{ mm} \times 2 \text{ mm}$ , 8-lead lead frame chip scale package [LFCSP] and is specified for operation from  $-55^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$ .

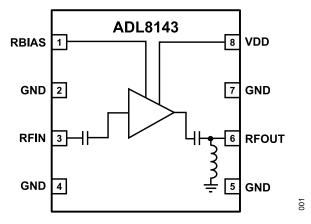

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1. Functional Block Diagram

# **TABLE OF CONTENTS**

| Features 1                             | Pin Configuration and Function Descriptions 5 |

|----------------------------------------|-----------------------------------------------|

| Applications1                          | Interface Schematics5                         |

| General Description1                   | Typical Performance Characteristics6          |

| Functional Block Diagram1              | Theory of Operation13                         |

| Specifications3                        | Applications Information14                    |

| 8 GHz to 10 GHz Frequency Range 3      | Recommended Bias Sequencing14                 |

| 10 GHz to 14 GHz Frequency Range 3     | Using RBIAS as a Fast Enable and Disable      |

| DC Specifications3                     | Function15                                    |

| Absolute Maximum Ratings4              | Recommended Power Management Circuit16        |

| Thermal Resistance4                    | Outline Dimensions17                          |

| Electrostatic Discharge (ESD) Ratings4 | Ordering Guide17                              |

| ESD Caution4                           | Evaluation Boards17                           |

# **REVISION HISTORY**

7/2024—Revision 0: Initial Version

analog.com Rev. 0 | 2 of 17

## **SPECIFICATIONS**

## **8 GHZ TO 10 GHZ FREQUENCY RANGE**

Supply voltage  $(V_{DD}) = 1.5 \text{ V}$ , quiescent current  $(I_{DQ}) = 35 \text{ mA}$ , bias resistance  $(R_{BIAS}) = 487 \Omega$ , and  $T_{CASE} = 25^{\circ}C$ , unless otherwise noted.

Table 1. 8 GHz to 10 GHz Frequency Range

| Parameter                                  | Min  | Тур   | Max | Unit  | Test Conditions/Comments                                                |

|--------------------------------------------|------|-------|-----|-------|-------------------------------------------------------------------------|

| FREQUENCY RANGE                            | 8    |       | 10  | GHz   |                                                                         |

| GAIN                                       | 26.5 | 28.5  |     | dB    |                                                                         |

| Gain Variation over Temperature            |      | 0.026 |     | dB/°C |                                                                         |

| NOISE FIGURE                               |      | 1     |     | dB    |                                                                         |

| RETURN LOSS                                |      |       |     |       |                                                                         |

| Input (S11)                                |      | 11    |     | dB    |                                                                         |

| Output (S22)                               |      | 19    |     | dB    |                                                                         |

| OUTPUT                                     |      |       |     |       |                                                                         |

| OP1dB                                      | 5.5  | 7.5   |     | dBm   |                                                                         |

| Saturated Output Power (P <sub>SAT</sub> ) |      | 9     |     | dBm   |                                                                         |

| OIP3                                       |      | 19.5  |     | dBm   | Measurement taken at output power (P <sub>OUT</sub> ) per tone = -6 dBm |

| Second-Order Intercept (OIP2)              |      | 14    |     | dBm   | Measurement taken at P <sub>OUT</sub> per tone = −6 dBm                 |

| POWER ADDED EFFICIENCY (PAE)               |      | 15.53 |     | %     | Measured at P <sub>SAT</sub>                                            |

# 10 GHZ TO 14 GHZ FREQUENCY RANGE

$V_{DD}$  = 1.5 V,  $I_{DQ}$  = 35 mA,  $R_{BIAS}$  = 487  $\Omega$ , and  $T_{CASE}$  = 25°C, unless otherwise noted.

Table 2. 10 GHz to 14 GHz Frequency Range Specifications

| Parameter                       | Min  | Тур   | Max | Unit  | Test Conditions/Comments                                |

|---------------------------------|------|-------|-----|-------|---------------------------------------------------------|

| FREQUENCY RANGE                 | 10   |       | 14  | GHz   |                                                         |

| GAIN                            | 26.5 | 28.5  |     | dB    |                                                         |

| Gain Variation over Temperature |      | 0.029 |     | dB/°C |                                                         |

| NOISE FIGURE                    |      | 1.1   |     | dB    |                                                         |

| RETURN LOSS                     |      |       |     |       |                                                         |

| S11                             |      | 17    |     | dB    |                                                         |

| S22                             |      | 15    |     | dB    |                                                         |

| OUTPUT                          |      |       |     |       |                                                         |

| OP1dB                           | 6.5  | 8.5   |     | dBm   |                                                         |

| P <sub>SAT</sub>                |      | 10    |     | dBm   |                                                         |

| OIP3                            |      | 22    |     | dBm   | Measurement taken at P <sub>OUT</sub> per tone = −6 dBm |

| OIP2                            |      | 22.5  |     | dBm   | Measurement taken at P <sub>OUT</sub> per tone = −6 dBm |

| PAE                             |      | 19.91 |     | %     |                                                         |

## **DC SPECIFICATIONS**

Table 3. DC Specifications

| Parameter                                       | Min | Тур  | Max | Unit |

|-------------------------------------------------|-----|------|-----|------|

| SUPPLY CURRENT                                  |     |      |     |      |

| $I_{DQ}$                                        |     | 35   |     | mA   |

| Amplifier Current (I <sub>DQ_AMP</sub> )        |     | 33.2 |     | mA   |

| R <sub>BIAS</sub> Current (I <sub>RBIAS</sub> ) |     | 1.8  |     | mA   |

| SUPPLY VOLTAGE                                  |     |      |     |      |

| $V_{DD}$                                        | 1.2 | 1.5  | 3.5 | V    |

analog.com Rev. 0 | 3 of 17

### **ABSOLUTE MAXIMUM RATINGS**

Table 4. Absolute Maximum Ratings

| Tubic 4: Aboolute muximum rutingo                                                                                            |                 |

|------------------------------------------------------------------------------------------------------------------------------|-----------------|

| Parameter                                                                                                                    | Rating          |

| $V_{DD}$                                                                                                                     | 4 V             |

| RF Input Power (RF <sub>IN</sub> )                                                                                           | 20 dBm          |

| Continuous Power Dissipation ( $P_{DISS}$ ), $T_{CASE}$ = 85°C (Derate 10.6 mW/°C Above 85°C)                                | 0.95 W          |

| Temperature                                                                                                                  |                 |

| Storage Range                                                                                                                | -65°C to +150°C |

| Operating Range                                                                                                              | -55°C to +125°C |

| Quiescent Channel ( $T_{CASE} = 85^{\circ}C$ , $V_{DD} = 1.5 V$ , $I_{DQ} = 35 \text{ mA}$ , Input Power ( $P_{IN}$ ) = Off) | 89.95°C         |

| Maximum Channel                                                                                                              | 175°C           |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.

$\theta_{\text{JC}}$  is the channel-to-case thermal resistance.

Table 5. Thermal Resistance

| Package Type                                      | $\theta_{JC}$ | Unit |  |

|---------------------------------------------------|---------------|------|--|

| CP-8-30                                           |               |      |  |

| Quiescent, T <sub>CASE</sub> = 25°C               | 80.4          | °C/W |  |

| Worst Case, <sup>1</sup> T <sub>CASE</sub> = 85°C | 94.3          | °C/W |  |

Worst case across all specified operating conditions.

# **ELECTROSTATIC DISCHARGE (ESD) RATINGS**

The following ESD information is provided for handling of ESD-sensitive devices in an ESD-protected area only.

Human body model (HBM) per ANSI/ESDA/JEDEC JS-001.

## **ESD Ratings for ADL8143**

Table 6. ADL8143. 8-Lead LFCSP

| ESD Model | Withstand Threshold (V) | Class |

|-----------|-------------------------|-------|

| НВМ       | ±300                    | 1A    |

### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

analog.com Rev. 0 | 4 of 17

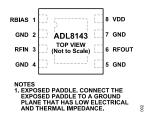

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 2. Pin Configuration

Table 7. Pin Function Descriptions

| Pin No.    | Mnemonic         | Description                                                                                                                                                                                                                                                                       |

|------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

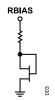

| 1          | RBIAS            | Bias Setting Resistor. Connect a resistor between RBIAS and VDD to set the I <sub>DQ</sub> . See Figure 49 and Table 8 for more details. See Figure 3 for the interface schematic.                                                                                                |

| 2, 4, 5, 7 | GND              | Ground. Connect to a ground plane that has low electrical and thermal impedance. See Figure 6 for the interface schematic.                                                                                                                                                        |

| 3          | RFIN             | RF Input. The RFIN pin is AC-coupled and matched to 50 $\Omega$ . See Figure 4 for the interface schematic.                                                                                                                                                                       |

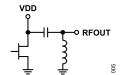

| 6          | RFOUT            | RF Output. The RFOUT pin has a resistive path to ground and an AC-coupling capacitor in the RF signal path and matched to 50 $\Omega$ . If the DC bias level of the next stage is not equal to 0 V, externally AC-couple the RFOUT pin. See Figure 5 for the interface schematic. |

| 8          | VDD              | Drain Bias. Connect the VDD pin to the supply voltage. See Figure 5 for the interface schematic.                                                                                                                                                                                  |

|            | GROUND<br>PADDLE | Ground Paddle. Connect the ground paddle to a ground plane that has low electrical and thermal impedance.                                                                                                                                                                         |

## **INTERFACE SCHEMATICS**

Figure 3. RBIAS Interface Schematic

REIN o—| ├── §

Figure 4. RFIN Interface Schematic

Figure 5. RFOUT/VDD Interface Schematic

Figure 6. GND Interface Schematic

analog.com Rev. 0 | 5 of 17

### TYPICAL PERFORMANCE CHARACTERISTICS

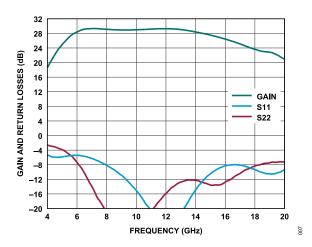

Figure 7. Gain and Return Loss vs. Frequency, 4 GHz to 20 GHz,  $V_{DD}$  = 1.5 V,  $I_{DQ}$  = 35 mA, and  $R_{BIAS}$  = 487  $\Omega$

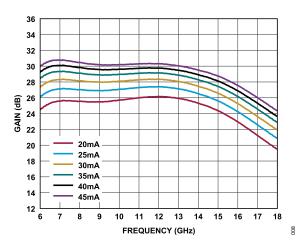

Figure 8. Gain vs. Frequency for Various  $I_{DQ}$ ,  $V_{DD}$  = 1.5 V

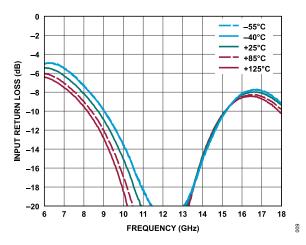

Figure 9. Input Return Loss vs. Frequency for Various Temperatures,  $V_{DD}$  = 1.5 V,  $I_{DQ}$  = 35 mA, and  $R_{BIAS}$  = 487  $\Omega$

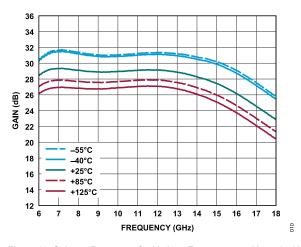

Figure 10. Gain vs. Frequency for Various Temperatures,  $V_{DD}$  = 1.5 V,  $I_{DQ}$  = 35 mA, and  $R_{BIAS}$  = 487  $\Omega$

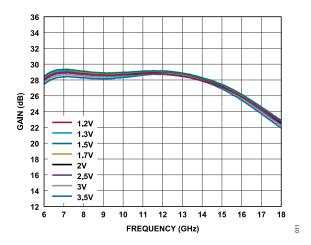

Figure 11. Gain vs. Frequency for Various Supply Voltages,  $I_{DQ}$  = 35 mA

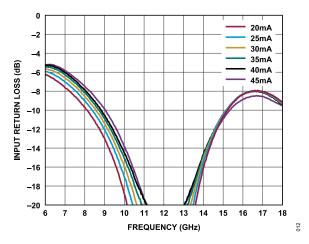

Figure 12. Input Return Loss vs. Frequency for Various  $I_{DQ}$ ,  $V_{DD}$  = 1.5 V

analog.com Rev. 0 | 6 of 17

### TYPICAL PERFORMANCE CHARACTERISTICS

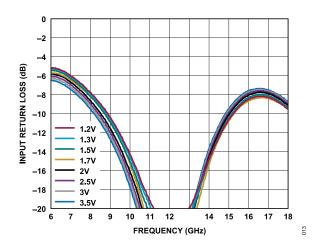

Figure 13. Input Return Loss vs. Frequency for Various Supply Voltages,  $I_{DQ} = 35 \text{ mA}$

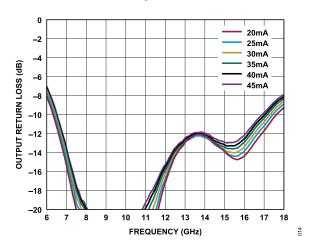

Figure 14. Output Return Loss vs. Frequency for Various  $I_{DQ}$ ,  $V_{DD}$  = 1.5 V

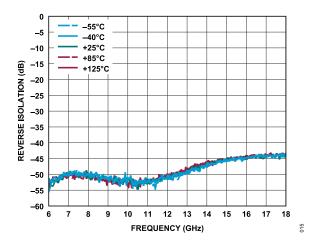

Figure 15. Reverse Isolation vs. Frequency for Various Temperatures,  $V_{DD}$  = 1.5 V,  $I_{DQ}$  = 35 mA, and  $R_{BIAS}$  = 487  $\Omega$

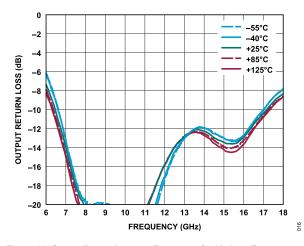

Figure 16. Output Return Loss vs. Frequency for Various Temperatures,  $V_{DD}$  = 1.5 V,  $I_{DO}$  = 35 mA, and  $R_{BIAS}$  = 487  $\Omega$

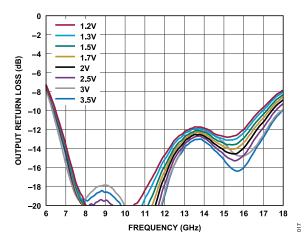

Figure 17. Output Return Loss vs. Frequency for Various Supply Voltages,  $I_{DQ} = 35 \text{ mA}$

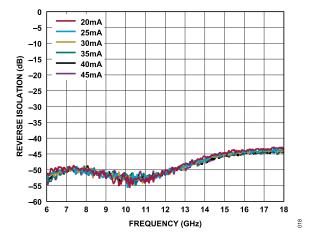

Figure 18. Reverse Isolation vs. Frequency for Various  $I_{DQ}$ ,  $V_{DD}$  = 1.5 V

analog.com Rev. 0 | 7 of 17

### **TYPICAL PERFORMANCE CHARACTERISTICS**

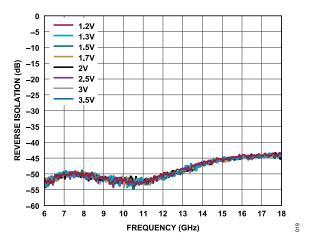

Figure 19. Reverse Isolation vs. Frequency for Various Supply Voltages,  $I_{DQ} = 35 \text{ mA}$

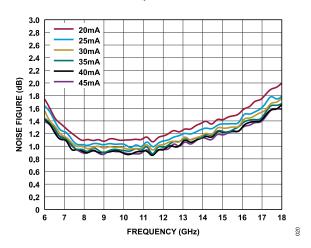

Figure 20. Noise Figure vs. Frequency for Various  $I_{\rm DQ}$ ,  $V_{\rm DD}$  = 1.5 V

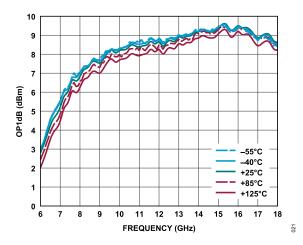

Figure 21. OP1dB vs. Frequency for Various Temperatures,  $V_{DD}$  = 1.5 V,  $I_{DQ}$  = 35 mA, and  $R_{BIAS}$  = 487  $\Omega$

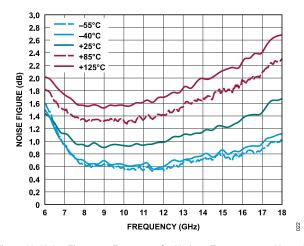

Figure 22. Noise Figure vs. Frequency for Various Temperatures,  $V_{DD}$  = 1.5 V,  $I_{DQ}$  = 35 mA, and  $R_{BIAS}$  = 487  $\Omega$

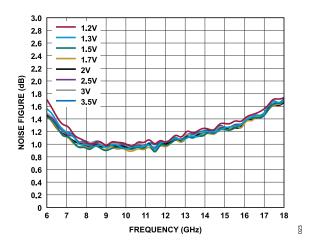

Figure 23. Noise Figure vs. Frequency for Various Supply Voltages,  $I_{DQ} = 35 \text{ mA}$

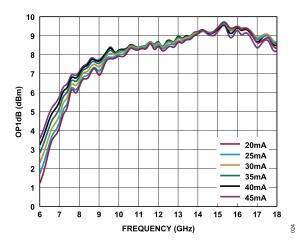

Figure 24. OP1dB vs. Frequency for Various  $I_{DQ}$ ,  $V_{DD} = 1.5 \text{ V}$

analog.com Rev. 0 | 8 of 17

### **TYPICAL PERFORMANCE CHARACTERISTICS**

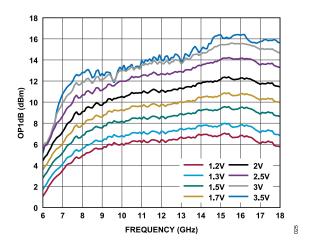

Figure 25. OP1dB vs. Frequency for Various Supply Voltages,  $I_{DQ}$  = 35 mA

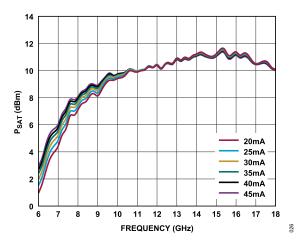

Figure 26.  $P_{SAT}$  vs. Frequency for Various  $I_{DQ}$ ,  $V_{DD}$  = 1.5 V

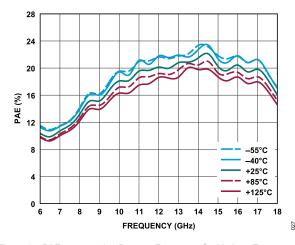

Figure 27. PAE measured at  $P_{SAT}$  vs. Frequency for Various Temperatures,  $V_{DD}$  = 1.5 V,  $I_{DQ}$  = 35 mA, and  $R_{BIAS}$  = 487  $\Omega$

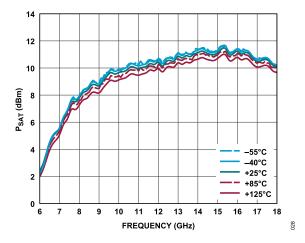

Figure 28.  $P_{SAT}$  vs. Frequency for Various Temperatures,  $V_{DD}$  = 1.5 V,  $I_{DO}$  = 35 mA, and  $R_{BIAS}$  = 487  $\Omega$

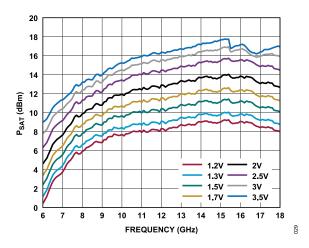

Figure 29. P<sub>SAT</sub> vs. Frequency for Various Supply Voltages, I<sub>DQ</sub> = 35 mA

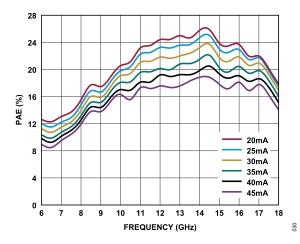

Figure 30. PAE Measured at  $P_{SAT}$  vs. Frequency for Various  $I_{DQ}$ ,  $V_{DD}$  = 1.5 V

analog.com Rev. 0 | 9 of 17

### **TYPICAL PERFORMANCE CHARACTERISTICS**

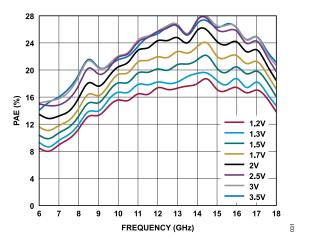

Figure 31. PAE Measured at  $P_{SAT}$  vs. Frequency for Various Supply Voltages,  $I_{DQ}$  = 35 mA

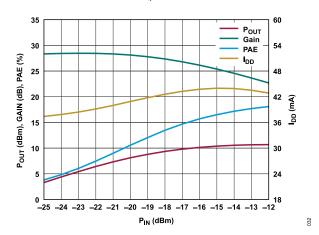

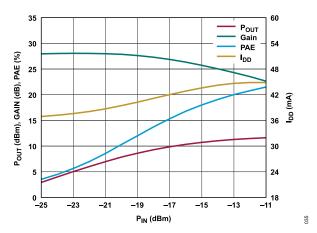

Figure 32.  $P_{OUT}$ , Gain, PAE, and  $I_{DD}$  vs.  $P_{IN}$ , Power Compression at 10 GHz,  $V_{DD}$  = 1.5 V, and  $R_{BIAS}$  = 487  $\Omega$

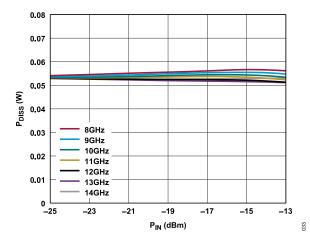

Figure 33.  $P_{DISS}$  vs.  $P_{IN}$  at Various Frequencies,  $T_{CASE}$  = 85°C and  $V_{DD}$  = 1.5 V

Figure 34.  $P_{OUT}$ , Gain, PAE, and  $I_{DD}$  vs.  $P_{IN}$ , Power Compression at 8 GHz,  $V_{DD}$  = 1.5 V, and  $R_{BIAS}$  = 487  $\Omega$

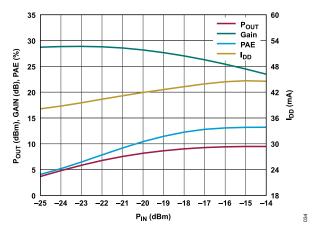

Figure 35.  $P_{OUT}$ , Gain, PAE, and  $I_{DD}$  vs.  $P_{IN}$ , Power Compression at 14 GHz,  $V_{DD}$  = 1.5 V, and  $R_{BIAS}$  = 487  $\Omega$

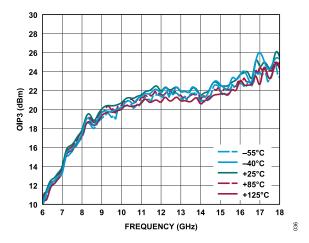

Figure 36. OIP3 vs. Frequency for Various Temperatures,  $V_{DD}$  = 1.5 V,  $I_{DQ}$  = 35 mA, and  $R_{BIAS}$  = 487  $\Omega$

analog.com Rev. 0 | 10 of 17

### TYPICAL PERFORMANCE CHARACTERISTICS

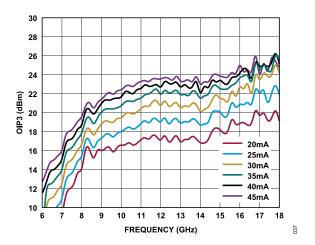

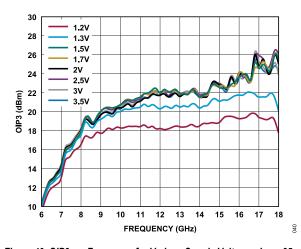

Figure 37. OIP3 vs. Frequency for Various  $I_{DQ}$ ,  $V_{DD}$  = 1.5 V

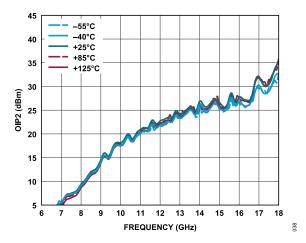

Figure 38. OIP2 vs. Frequency for Various Temperatures,  $V_{DD}$  = 1.5 V,  $I_{DO}$  = 35 mA, and  $R_{BIAS}$  = 487  $\Omega$

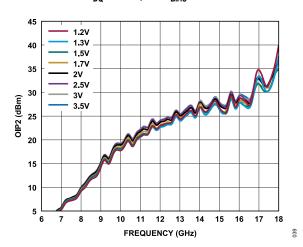

Figure 39. OIP2 vs. Frequency for Various Supply Voltages, IDQ = 35 mA

Figure 40. OIP3 vs. Frequency for Various Supply Voltages,  $I_{DQ}$  = 35 mA

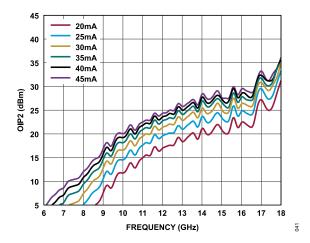

Figure 41. OIP2 vs. Frequency for Various  $I_{DQ}$ ,  $V_{DD}$  = 1.5 V

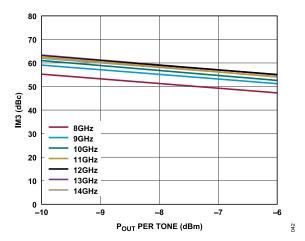

Figure 42. IM3 vs.  $P_{OUT}$  Per tone for Various Frequencies,  $V_{DD}$  = 1.5 V and  $R_{BIAS}$  = 487  $\Omega$

analog.com Rev. 0 | 11 of 17

## **TYPICAL PERFORMANCE CHARACTERISTICS**

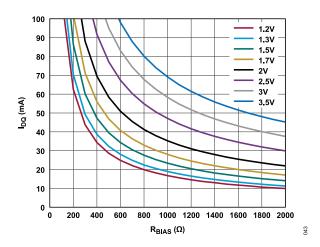

Figure 43.  $I_{DQ}$  vs.  $R_{BIAS}$  at Various Supply Voltages, 0  $\Omega$  to 2  $k\Omega$

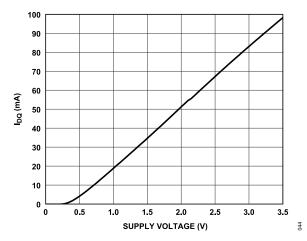

Figure 44.  $I_{DQ}$  vs. Supply Voltage,  $R_{BIAS}$  = 487  $\Omega$

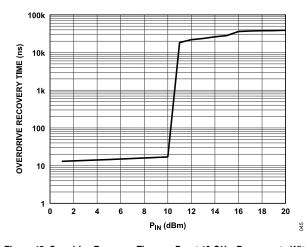

Figure 45. Overdrive Recovery Time vs.  $P_{IN}$  at 12 GHz, Recovery to Within 90% of Small Signal Gain Value,  $V_{DD}$  = 1.5 V, and  $R_{BIAS}$  = 487 $\Omega$

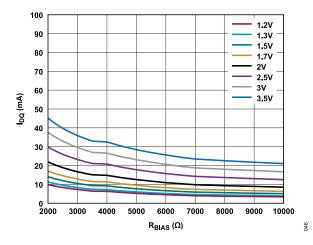

Figure 46.  $I_{DQ}$  vs.  $R_{BIAS}$  at Various Supply Voltages, 2 k $\Omega$  to 10 k $\Omega$

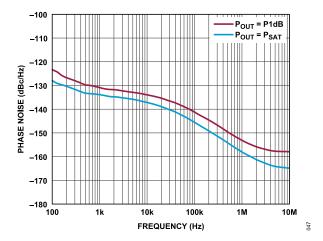

Figure 47. Phase Noise vs. Frequency at 10 GHz for Various  $P_{\text{OUT}}$  Values

analog.com Rev. 0 | 12 of 17

### THEORY OF OPERATION

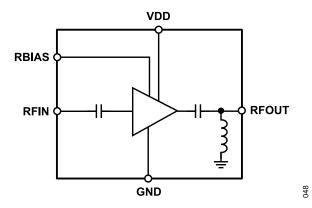

The ADL8143 is a wideband LNA that operates from 8 GHz to 14 GHz. A simplified block diagram is shown in Figure 48.

The ADL8143 has internally AC-coupled, single-ended input and output ports with an impedance that is nominally equal to 50  $\Omega$  over the specified frequency range. While the RF output path is AC-coupled, there is a DC path to ground on the RFOUT side of the AC-coupling capacitor. No external matching components are required. To adjust  $I_{DQ}$ , connect an external resistor near the RBIAS pin.

Figure 48. Simplified Schematic

analog.com Rev. 0 | 13 of 17

# **APPLICATIONS INFORMATION**

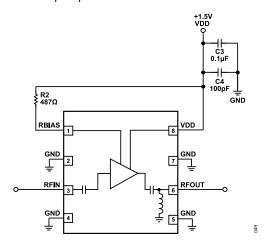

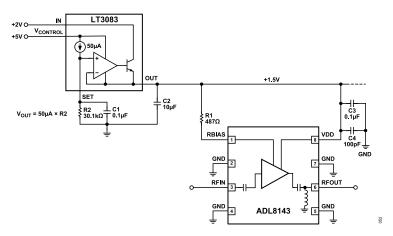

The basic connections for operating the ADL8143 from 8 GHz to 14 GHz are shown in Figure 49. No external biasing inductor is required, allowing a 1.5 V supply to be connected to the VDD pin. It is recommended to use 0.1  $\mu$ F and 100 pF power supply decoupling capacitors. The power supply decoupling capacitors shown in Figure 49 represent the configuration used to characterize and qualify the ADL8143.

To set the  $I_{DQ}$ , connect a resistor, R2, between the RBIAS and VDD pins. A default value of 487  $\Omega$  is recommended that results in a nominal  $I_{DQ}$  of 35 mA. The RBIAS pin also draws a current that varies with the value of  $R_{BIAS}$ . Table 8 and Table 9 show the recommended  $R_{BIAS}$  values with the associated  $I_{DQ}$  values. Do not leave the RBIAS pin open.

Figure 49. Typical Application Circuit

#### RECOMMENDED BIAS SEQUENCING

The correct sequencing of the DC and RF power is required to safely operate the ADL8143. During power-up, apply  $V_{DD}$  before the RF power is applied to RFIN, and during power-off, remove the RF power from RFIN before  $V_{DD}$  is powered off.

Table 8. Recommended Bias Resistor Values for Various  $I_{DQ}$  Values,  $V_{DD}$  = 1.5 V

| R <sub>BIAS</sub> (Ω) | I <sub>DQ</sub> (mA) | I <sub>DQ_AMP</sub> (mA) | I <sub>RBIAS</sub> (mA) |

|-----------------------|----------------------|--------------------------|-------------------------|

| 1171                  | 20                   | 19.1                     | 0.9                     |

| 835                   | 25                   | 23.8                     | 1.2                     |

| 629                   | 30                   | 28.5                     | 1.5                     |

| 487                   | 35                   | 33.1                     | 1.9                     |

| 398                   | 40                   | 37.8                     | 2.2                     |

| 329                   | 45                   | 42.4                     | 2.6                     |

Table 9. Recommended Bias Resistor Values for Various Supply Voltages,  $I_{DQ}$  = 35 mA

| R <sub>BIAS</sub> (Ω) | V <sub>DD</sub> (V) |

|-----------------------|---------------------|

| 295                   | 1.2                 |

| 356                   | 1.3                 |

| 487                   | 1.5                 |

| 652                   | 1.7                 |

| 933                   | 2.0                 |

| 1494                  | 2.5                 |

| 2190                  | 3.0                 |

| 3091                  | 3.5                 |

analog.com Rev. 0 | 14 of 17

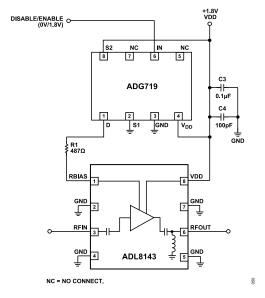

#### **USING RBIAS AS A FAST ENABLE AND DISABLE FUNCTION**

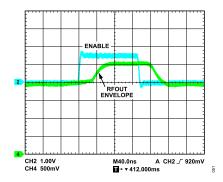

The RBIAS pin can be used as a fast enable and disable control input. By incorporating a single-pole, double throw (SPDT) switch to the RBIAS pin, an enable and/or disable circuit can be implemented as shown in Figure 50. The ADG719 complementary metal-oxide semiconductor (CMOS) switch is used to connect the RBIAS resistor between GND and 1.8 V. When the RBIAS resistor is connected to ground and the RF input level is -20 dBm, the overall current

consumption reduces to less than 1 mA. Figure 51 shows a plot of the turn on and/or turn off response time of the RF output envelope when the IN pin of the ADG719 is pulsed. Note that because the ADG719 has a minimum supply voltage of 1.8 V, the supply voltage for ADG719 and ADL8143 has been set to 1.8 V instead of 1.5 V to satisfy that requirement.

Figure 50. Fast Enable and Disable Using a 0 V to 1.8 V Pulse on the RBIAS Resistor

Figure 51. On and/or Off Response of the RFOUT Envelope When the IN Pin of the ADG719 Is Pulsed

analog.com Rev. 0 | 15 of 17

### RECOMMENDED POWER MANAGEMENT CIRCUIT

Figure 52 shows a recommended power management circuit that uses the LT3083 low dropout (LDO) regulator. The LT3083 output load current is supplied to the IN pin. Power for the on-board control is applied to the  $V_{CONTROL}$  pin. A voltage that is at least 1.4 V higher than the output voltage must be applied to the  $V_{CONTROL}$  pin. In Figure 52,  $V_{CONTROL}$  has been set to 5 V but could be set as low as 2.9 V for a 1.5 V output voltage. The current into the  $V_{CONTROL}$  pin is typically 1.7% of the total output current.

The LT3083 can provide up to 3 A of load current. In a phased array application, a single LT3083 can easily provide bus power for all of the ADL8143 devices in a 64-element array. A dropout voltage of

500 mV is assumed based on a load current of 3 A. If the required load current is lower, the voltage on the IN pin of the LT3083 can be reduced to improve efficiency. For example, for a load current of 1 A, the dropout voltage drops to a worst-case value of 160 mV.

For applications that require a lower dropout voltage, the LT3033 can be used. For a 3 A load, the worst-case dropout voltage is 240 mV in the LT3033.

Table 10 provides recommended resistor values to set the other output voltages. In each case, the minimum  $V_{\text{IN}}$  voltage is specified based on a 3 A load and a 500 mV dropout voltage.

Table 10. Recommended Resistor Values for the Various LDO Output Voltages

| LDO V <sub>OUT</sub> (V) | R2 (kΩ) | Minimum V <sub>DD</sub> (V) |

|--------------------------|---------|-----------------------------|

| 1.2                      | 24.3    | 1.7                         |

| 1.5                      | 30.1    | 2.0                         |

| 2.0                      | 40.2    | 2.5                         |

| 2.5                      | 49.9    | 3.0                         |

| 3.0                      | 60.4    | 3.5                         |

| 3.3                      | 66.5    | 3.8                         |

| 3.5                      | 69.8    | 4.0                         |

Figure 52. Recommended Power Management Circuit

analog.com Rev. 0 | 16 of 17

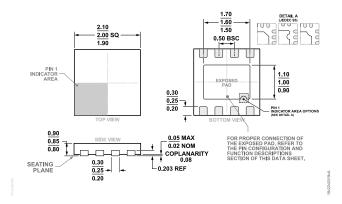

### **OUTLINE DIMENSIONS**

Figure 53. 8-Lead Lead Frame Chip Scale Package [LFCSP]

2 mm × 2 mm Body and 0.85 mm Package Height

(CP-8-30)

Dimensions shown in millimeters

## **ORDERING GUIDE**

| Model <sup>1,2</sup> | Temperature Range | Package Description                 | Packing Quantity | Package<br>Option |

|----------------------|-------------------|-------------------------------------|------------------|-------------------|

| ADL8143ACPZN         | -55°C to +125°C   | 8-Lead LFCSP, 2 mm × 2 mm × 0.85 mm | Tape, 1          | CP-8-30           |

| ADL8143ACPZN-R7      | -55°C to +125°C   | 8-Lead LFCSP, 2 mm × 2 mm × 0.85 mm | Reel, 3000       | CP-8-30           |

<sup>&</sup>lt;sup>1</sup> Z = RoHS Compliant Part.

## **EVALUATION BOARDS**

| Model <sup>1</sup> | Description      |

|--------------------|------------------|

| ADL8143-EVALZ      | Evaluation Board |

<sup>&</sup>lt;sup>1</sup> Z = RoHS Compliant Part.

<sup>&</sup>lt;sup>2</sup> The lead finish of ADL8143ACPZN and ADL8143ACPZN-R7 is nickel palladium gold.